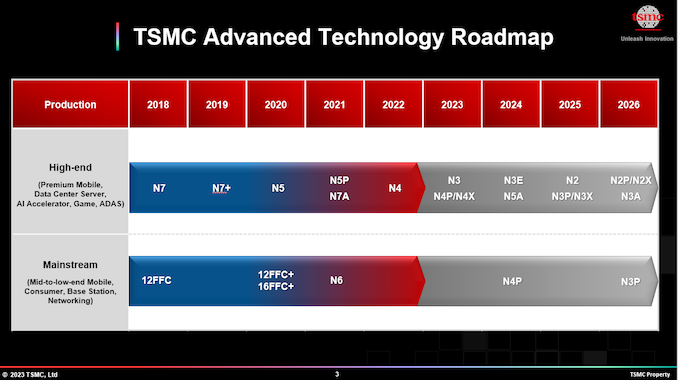

【锚思科技讯】在今天举行的2023年北美技术研讨会上,台积电披露了其在2025年至2026年及以后即将推出的N2 2nm级生产节点计划的更多细节。台积电的N2系列制造技术将随着更多的变化而扩展,包括具有背面功率传输的N2P和用于高性能计算的N2X。在这些即将到来的N2代工艺节点之间,台积电正在制定路线图,以继续其提高晶体管性能效率、优化功耗和提高晶体管密度的不懈步伐。

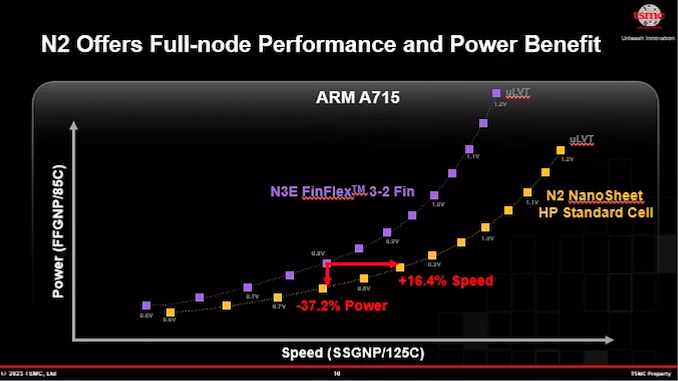

台积电去年推出的最初N2制造工艺将是该铸造厂第一个使用栅极全方位(GAAFET)晶体管的节点,台积电称之为纳米片晶体管。GAAFET相对于电流FinFET晶体管的优势包括降低的漏电流(因为通道的四侧都有闸门),以及调整沟道宽度以获得更高性能或更低功耗的能力。

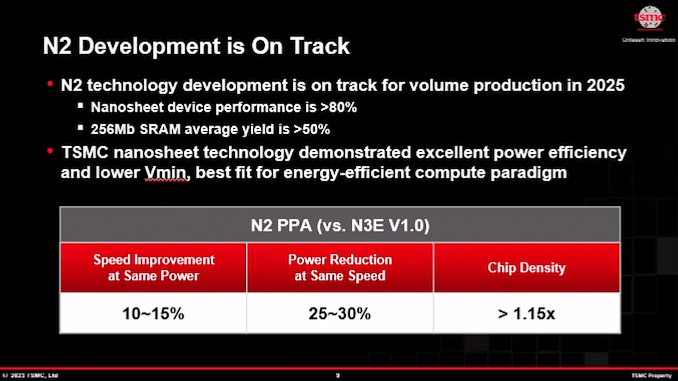

台积电在去年推出这项技术时表示,在相同的功率和复杂性下,它将使晶体管性能提高10%至15%,或者在相同的时钟和晶体管数量下,将功耗降低25%至30%。该公司还表示,N2将提供比N3E高15%以上的“混合”芯片密度,这比去年宣布的10%的密度增加了。

今天,该公司表示,N2技术开发正在步入正轨,该节点将在2025年(可能在2025年很晚)进入大批量生产。该公司还表示,在进入HVM的两年前,其Nanopheet GAA晶体管的性能达到了目标规格的80%以上,256Mb SRAM测试IC的平均产量超过了50%。

台积电的一份声明中写道:“台积电纳米片技术表现出优异的功率效率和更低的Vmin,最适合节能计算模式。”。

台积电的N2家族将在2026年的某个时候发展,届时该公司计划引入其N2P制造技术。将为N2的纳米片GAA晶体管添加背面电源导轨的N2P。

背面电源输送旨在通过将电源导轨移到背面来解耦I/O和电源布线,解决线路后端(BEOL)电阻升高等挑战。这反过来又将提高晶体管的性能并降低其功耗。此外,背面供电消除了数据和电源连接之间的一些潜在干扰。

背后的电源传递是一种创新,其重要性再怎么强调也不为过。芯片制造商多年来一直在与芯片功率输送电路中的电阻作斗争,而背面功率输送网络(PDN)是解决这些电阻的另一种方法。此外,去耦合PDN和数据连接也有助于减少面积,因此与N2相比,预计N2P将进一步增加晶体管密度。

目前,台积电没有透露任何关于N2P相对于N2的性能、功率和面积(PPA)优势的硬数据。但根据我们从行业消息来源了解到的情况,仅背面电源导轨就可以带来个位数的功率提升和两位数的晶体管密度提升。

台积电表示,N2P有望在2026年投入生产,因此我们可以推测,第一批基于N2P的芯片将在2027年上市。假设台积电能够在2024年按时交付自己的20A工艺,那么这一时间表将使台积电在背面电源方面落后竞争对手英特尔大约两年。

除了可能成为台积电2nm代工艺的主力军的N2P外,台积电也在准备N2X。这将是一个为高端CPU等高性能计算(HPC)应用量身定制的制造过程,这些应用需要增加电压和时钟。铸造厂没有概述该节点与N2、N2P和N3X相比的具体优势,但与所有性能增强节点一样,实际优势预计在很大程度上取决于实施了多少设计技术协同优化(DTCO)。