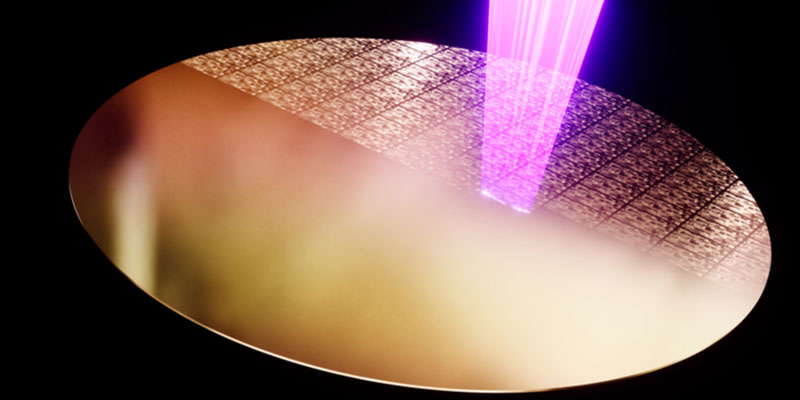

4月13日消息,韩媒《釜山日报》当地时间今日报道称,三星电子当前2nm工艺制程良率已达到55%上下,但这一水平不仅落后于台积电约一成,同时也未达到竞争重要无晶圆厂(Fabless)企业代工订单所需的标准,凸显出三星在先进半导体制程领域的竞争短板。

报道指出,当前媒体对芯片制程良率的报道往往仅提及百分比数据,却未明确对应的芯片面积,这一缺失导致良率数据的实际价值与可比性大幅不足。芯片良率与芯片面积呈现强烈的负相关性,在缺陷密度一定的情况下,芯片面积越大,包含缺陷的概率就越高,良率难度呈曲线式上升。

业内给出了较为极端的例子加以说明:在100mm²的芯片(移动端SoC级别)上取得90%良率的难度,远小于在600mm²芯片(旗舰AI XPU级别)上实现同等良率。这也意味着,单纯对比良率百分比,难以全面反映不同厂商先进制程的实际成熟度与竞争力。

更值得关注的是,业界人士进一步指出,若综合考虑性能分级筛选及后端封测流程带来的良率损失,以最终可交付成品计算,三星电子2nm工艺的实际良率将降至仅40%。这一数据表明,三星2nm制程节点目前仍未完全成熟,无法实现稳定批量交付,且受良率影响,其实际价格竞争力也相对不足。

据悉,当前三星2nm工艺仅能吸引个别成本敏感的小型企业尝试合作,难以获得主流Fabless企业的核心代工订单。反观台积电,其2nm工艺良率已稳定在60%-70%区间,具备更强的量产稳定性,已成功锁定苹果、高通、英伟达等核心客户,进一步拉开与三星的差距。

作为当前最先进的半导体制程节点之一,2nm工艺的良率直接决定企业代工业务的盈利能力,单块晶圆产出的合格芯片越多,单位成本就越低。三星此前为拉升2nm良率投入大量资源,虽实现从低位到55%的提升,但良率稳定性及实际成品率仍存在明显短板,短期内难以改变在高端代工市场的劣势地位。

三星2nm工艺的良率困境,不仅影响其代工业务的市场竞争力,也可能延缓其在先进制程领域的布局节奏。未来,若无法快速提升良率稳定性、缩小与台积电的差距,三星或将在2nm及后续1nm制程的竞争中进一步落后,难以撼动台积电在全球晶圆代工市场的主导地位。